半导体芯片全生命周期解析:制造、设计、测试与封装

半导体芯片,作为现代电子设备的核心,其制造过程复杂且精细,涉及众多专业术语和技术。本文旨在对半导体芯片的全生命周期进行详细解析,从制造、设计、测试到封装,为业内人士提供参考。

一、制造过程

半导体芯片的制造过程是高科技和精密工程的结晶。以下是一些关键术语:

TAPEOUT(TO):指提交最终GDSII文件给Foundry工厂进行加工的过程,是芯片制造的开始。

FULLMASK:全掩膜工艺,指制造流程中的全部掩膜都为某个设计服务,与MPW(多项目晶圆)相对,后者允许多个项目共享晶圆。

Foundry:晶圆厂,专门从事芯片制造的厂家,与Fabless(无晶圆厂的设计公司)相对。

Wafer:晶圆,是芯片制造的原材料,通常为圆形的薄硅片。

Die:晶圆切割后得到的单个芯片单元,需进一步封装。

Chip:最终封装后的芯片,是可以直接应用的成品。

Bump:凸点技术,用于倒装工艺封装,如flipchip。

Mask:掩膜,用于在硅片上选定区域进行遮盖,以便进行腐蚀或扩散。

二、设计过程

芯片设计是将创意转化为实际电路的过程,涉及以下关键概念:

Fabless:指没有制造业务、只专注于设计的集成电路公司。

RTL(Register-TransferLevel):硬件描述语言,用于描述同步数字电路。

SDC(SynopsysDesignConstraints):设计约束文件,指导综合工具将RTL转换成netlist。

Verification:芯片功能验证,确保RTL与referencemodel一致。

Simulation:仿真,用于模拟芯片功能和功耗,反映真实场景。

IP(IntellectualProperty):知识产权,指设计资产或已设计完成的功能电路模块。

三、测试过程

测试是确保芯片性能符合预期的重要步骤:

CP(ChipProbing):直接用晶圆划片机对晶圆进行测试,确保每个Die满足设计规格。

FT(FinalTest):芯片出厂前的最后一道测试,针对封装好的芯片。

Yield:良率,与工艺相关,影响芯片的失效机率。

四、封装过程

封装是芯片制造的最后阶段,涉及以下技术:

BGA(BallGridArray):表面安装封装技术,使用多个焊接球连接芯片。

ASIC(ApplicationSpecificIntegratedCircuit):为特定需求定制的专用集成电路。

Wirebonding:打线技术,通过金属丝连接芯片与引线框架。

Flipchip:倒装芯片技术,通过在I/Opad上沉积锡铅球与基板结合。

COB(Chip-on-Board):板上芯片封装,将裸芯片粘附在PCB上并进行引线键合。

SOC(SystemOnChip):片上系统,集成CPU、总线、外设等于一体的芯片。

SIP(SystemInPackage):系统级封装,集成不同功能的裸芯片于一个封装体内。

半导体芯片的制造是一个涉及众多技术和步骤的复杂过程。从设计到制造,再到测试和封装,每一个环节都至关重要,共同确保了芯片的性能和可靠性。随着技术的不断进步,半导体行业也在不断发展,为电子设备带来更强大的计算能力和更小的尺寸。

-

【光学前沿】阿尔托大学开创光涡旋新设计,推动光数据传输革命

在数据存储和传输需求日益增长的今天,寻找更高效的方法来编码和传输大量数据变得至关重要。阿尔托大学的最新研究成果为我们提供了一种创新的解决方案:通过在光纤中使用准晶体传输数据的光涡旋。这项突破性的设计方法不仅理论上可以创建任何类型的光涡旋,而且在实际应用中展示了极高的拓扑电荷,为光数据传输开辟了新的可能性

2024-11-22

-

半导体芯片全生命周期解析:制造、设计、测试与封装

半导体芯片,作为现代电子设备的核心,其制造过程复杂且精细,涉及众多专业术语和技术。本文旨在对半导体芯片的全生命周期进行详细解析,从制造、设计、测试到封装,为业内人士提供参考。

2024-11-22

-

激光束投射阴影:渥太华大学与布鲁克海文国家实验室的创新发现

近日,在光学领域的一项突破性研究中,渥太华大学和布鲁克海文国家实验室的研究人员展示了激光束在特定条件下能够像实体物体一样投射出可见阴影。这一发现不仅挑战了我们对光和阴影的传统认知,也为激光技术的应用开辟了新的可能性。

2024-11-21

-

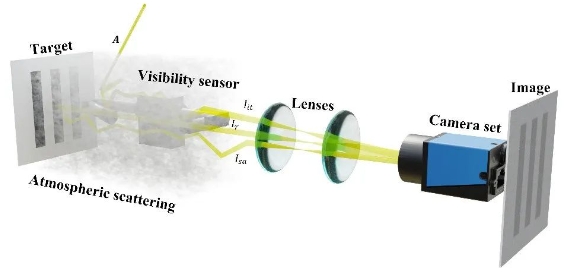

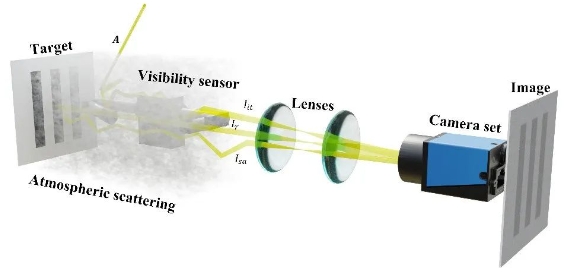

【光学前沿】中山大学研究团队突破大气散射光学成像极限

光学成像技术在遥感、天文学、军事监控和环境监测等多个领域扮演着关键角色。然而,光线在通过大气散射介质时,会受到空气中颗粒物的干扰,导致图像对比度和清晰度大幅下降,影响远距离目标的观测和识别。因此,提高在恶劣天气条件下光学成像系统的性能,是光学成像领域亟待解决的挑战。

2024-11-21